StreamDSP Announces Version 4.2 of sFPDP Gen3 (VITA 17.3) IP Core with Low-Level Copy Mode, Lattice Avant Support, and Expanded FEC Capability

COLUMBUS, OH, UNITED STATES, April 22, 2026 /EINPresswire.com/ — StreamDSP Announces Version 4.2 of sFPDP Gen3 (VITA 17.3) IP Core with Low-Level Copy Mode, Lattice Avant Support, and Expanded FEC Capability

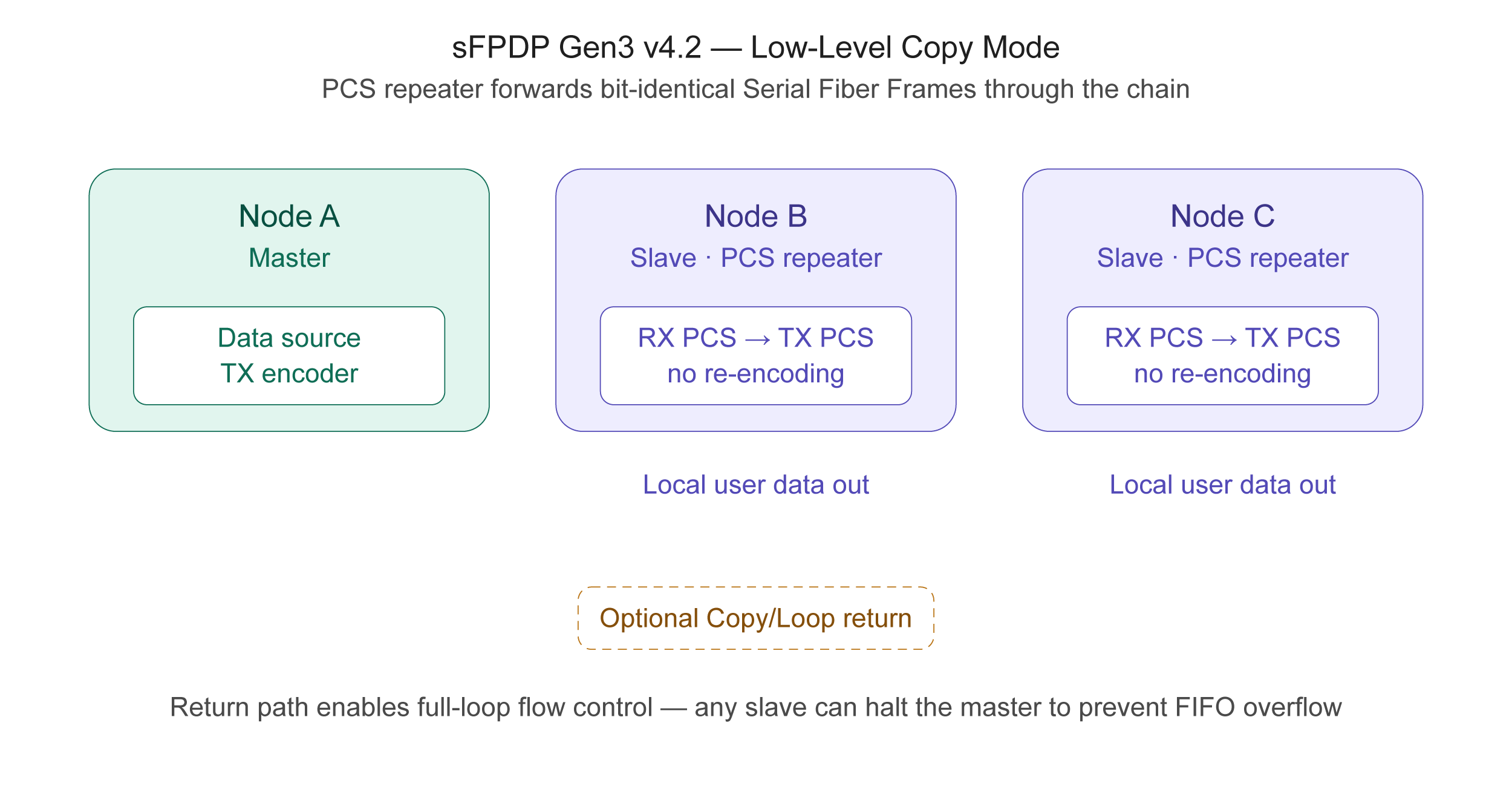

Today, StreamDSP LLC, an Intellectual Property (IP) provider specializing in high-speed sFPDP IP cores for FPGAs and ASICs, announced the immediate availability of version 4.2 of its sFPDP Gen3 (VITA 17.3) IP Core. The v4.2 release introduces a new Low-Level Copy Mode based on a PCS-layer repeater, adds support for Lattice Avant FPGAs, and extends the core’s Forward Error Correction feature set with uncorrectable block detection. Additional improvements include PCS link diagnostic status outputs, improved flow-control and Skip-word detection, and majority-vote PCS error resiliency on links with three or more lanes. All netlist deliveries are now provided as IEEE 1735 encrypted source for significantly faster simulation times.

“Customers deploying sFPDP in daisy-chained and ring topologies have been asking for a cleaner way to forward data without re-encoding it at every node,” said StreamDSP CTO, Brian Kahlig. “The new Low-Level Copy Mode uses a repeater function inside the Interlaken Framing Layer to guarantee that the retransmitted Serial Fiber Frames are bit-identical to those received, eliminating the re-framing variability of the previous High-Level Copy Mode. Combined with our new Lattice Avant support, the v4.2 release gives designers more topology options and more vendor choices than any other sFPDP IP on the market.”

The StreamDSP sFPDP Gen3 IP Core provides a high-speed, low-latency, low-overhead serial link used in defense, aerospace, data acquisition, machine vision, signal processing, and high-performance computing applications. The core supports any number of bonded channels, runs at any rate supported by the FPGA transceiver, and shares a single common user interface across Altera/Intel, Xilinx/AMD, Lattice, and Microsemi device families — allowing designers to connect FPGAs from different vendors with no protocol translation required. With the optional StreamFEC add-on, v4.2 also delivers Reed-Solomon (255,239) forward error correction for a net coding gain of 5.8 dB at 10⁻¹³ BER with less than 8.5% bandwidth overhead, now including detection of uncorrectable 255-word symbol blocks for enhanced link-health reporting.

To facilitate rapid customer integration and ensure success, StreamDSP provides hardware-tested example designs, simulation models, and testbench environments for every supported FPGA family, including a new Lattice Avant Versa-G development board design. Every IP sale includes 12 months of support and maintenance. StreamDSP’s customer base includes defense, aerospace, industrial, and educational institutions. StreamDSP also provides customized engineering design and integration services.

About StreamDSP LLC: StreamDSP LLC is an Intellectual Property and Engineering Services company based in Columbus, OH. Founded in 2007, StreamDSP has designed Interlaken and Serial Front Panel Data Port (sFPDP) IP cores for FPGAs and ASICs. StreamDSP provides ongoing support and maintenance for their large customer base and also offers custom engineering design services.

Brian Kahlig

StreamDSP LLC

+1 855-377-3742

email us here

Visit us on social media:

LinkedIn

Facebook

Legal Disclaimer:

EIN Presswire provides this news content “as is” without warranty of any kind. We do not accept any responsibility or liability

for the accuracy, content, images, videos, licenses, completeness, legality, or reliability of the information contained in this

article. If you have any complaints or copyright issues related to this article, kindly contact the author above.

![]()

Media gallery